本系列主要介绍视频编解码芯片的设计,以HEVC视频编码标准为基础,简要介绍编解码芯片的整体硬件架构设计以及各核心模块的算法优化与硬件流水线设计。本文介绍视频编码芯片的敏佳架构设计思想和XK265 编解码器的层次结构。

相比于其他应用,视频编解码的一大特点是对于实时性的要求极高,而软件通常难以达到这一目标,因此几乎所有相关设备,如监控探头、摄像机、手机和计算机等,都会配备硬编硬解芯片。而不同的设备平台对于视频编解码的需求是迥然不同的,即便是同一设备平台,在不同的应用场景下,其对于视频编解码的需求也不尽相同。不同的应用需求,就要求视频编解码架构能够敏捷化地进行配置。

1敏捷架构

软件算法在架构和行为上不会考虑硬件实现中的相应限制,往往难以在硬件平台上发挥出原有的表现。而硬件算法方面,单个模块的研究成果在架构和行为上若不考虑整体实现时的系统限制,也往往难以在整体架构中发挥出原有的表现。

从整体系统出发,为了能够尽可能地优化面积、时序和功耗等指标,并且能够针对不同的编解码需求灵活地配置系统,有必要采用一种敏捷的芯片架构。这里的“敏捷”是一种设计理念,可以理解为一种可重构性、可配置性,并且分为静态和动态两类。

静态是指对尚未生产的芯片进行配置,以改变芯片所支持的功能集合,并进而改变芯片的面积、(最高)频率、功耗、(最高)质量和(最高)性能等指标。其主要意义在于可以敏捷地针对不同档次的平台提供不同档次的芯片,从而达到效益的最大化。相比于重新设计一个芯片,静态敏捷设计能够有效地减少芯片的NRE (Non-Recurring Engineering) 成本和TTM (Time To Market)周期,而这对于芯片量产来说是至关重要的。

动态是指对已经生成的芯片进行配置,以改变芯片所执行的当前功能,并进而改变编码的(工作)频率、(工作)功耗、(工作)质量和(工作)性能等指标。其主要意义在于可以动态地针对不同档次的场景提供不同档次的行为,从而达到功能的最大化。相比于只有某个单一功能,动态敏捷设计能够向客户提供质量与性能在不同比重上的权衡,而这对于芯片使用来说是至关重要的。

2可配置的模块设计

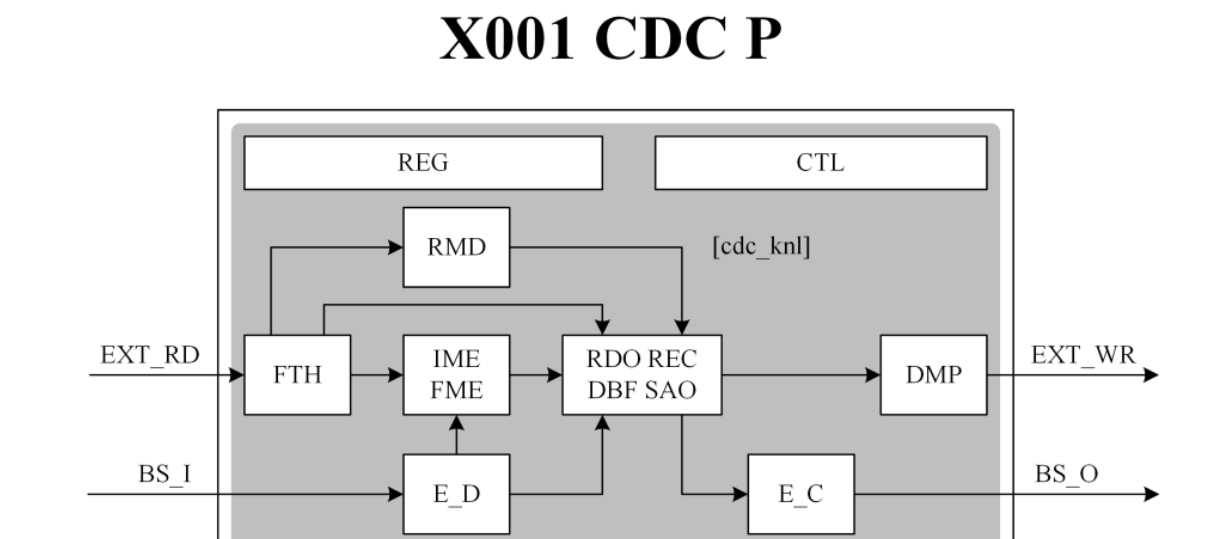

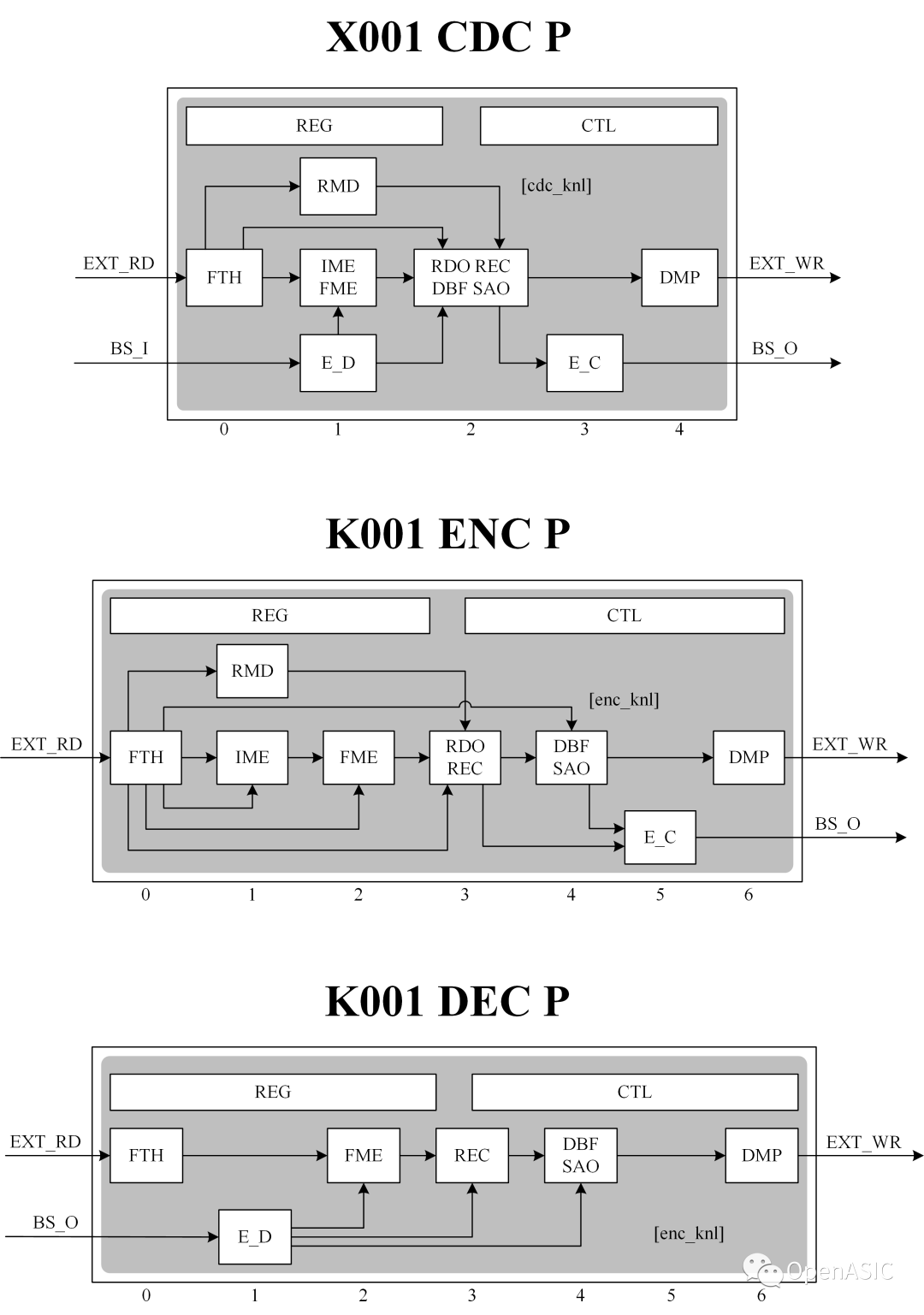

编解码器的主要模块有FTH(读取像素)、RMD(粗略模式估计)、IME(整像素运动估计)、FME(分像素运动估计)、RDO(率失真优化)、REC(重建)、DBF(方块滤波)、SAO(样点自适应补偿)、E_C(熵编码)、E_D(熵解码)、DMP(写出像素)等。

丰富的可配置项对于敏捷架构设计非常重要。下表1总结了敏捷架构下,部分底层模块的静态和动态可配置参数。

表1

|

模块名称 |

静态可配置 |

动态可配置 |

|

RMD |

1. 引擎数量 |

1. 被搜索的PU大小 |

|

IME |

1. 阵列大小 |

1. 被搜索的图案 |

|

FME |

1. 引擎数量 |

1. 被搜索的PU大小 |

|

RDO |

1. 引擎大小 |

1. 被遍历的帧内预测模式数量 |

3 XK265编解码器

XK265是一款具有敏捷架构的视频编解码器,其层次结构能够高效地配置视频编解码器的行为。基于敏捷的芯片架构,可以很容易地定制单一编码器、单一解码器或复合编解码器,以及支持单一I帧版本或支持I帧和P帧版本的不同IP核,同时也可以定制生成不同性能指标、面积指标、压缩率指标的专用编码器IP核。

作为一款具有敏捷架构的视频编解码器,XK265 RTL已经包含了12个变种,分别是X001 CDC I、X001 CDC P、X001 ENC I、X001 ENC P、X001 DEC I、X001 DEC P、K001 CDC I、K001 CDC P、K001 ENC I、K001 ENC P、K001 DEC I和K001 DEC P。其中,001表示第一个版本,以HEVC标准为依托;X表示针对ASIC平台,K表示针对FPGA平台;CDC表示支持编解码(encoder和decoder),ENC表示支持编码(encoder),DEC表示支持解码(decoder);I表示支持帧内帧、P表示同时支持帧内帧和帧间帧。

以X001CDC P、K001 ENC P和K001 DEC P作为敏捷架构的IP定制的例子,下表2总结了相关的参数。

表2

|

型号 |

X001 CDC P |

K001 ENC P |

K001 DEC P |

|

目标频率 |

800MHz |

140MHz |

120 MHz |

|

性能 |

4K@30fps |

4K@30fps |

4K@30fps |

|

流水线 |

五级 |

七级 |

七级 |

其中,X001CDC P是一款面向于ASIC平台的极低代价、较高性能、较高质量的视频编解码器;K001 ENC P是一款面向于FPGA平台的极低代价、极高性能、中下质量的视频编码器;K001 DEC P是一款面向于FPGA平台的极低代价、极高性能的视频解码器。它们的架构如下图1所示。

图1